# 40Gb/s QSFP Active Copper TC-QQCOy-V00

## **Product Brief Introduction**

# **Features**

- Hot pluggable QSFP active cable assembly

- 4 independent duplex channels operating at 10Gbps, also support for 2.5Gbps, 5Gbps data rates

- Proven Link length up to 15 meters over 26AWG cables

- Compliant QSFP MSA specifications

- Operating case temperature: -40 to 85°C

- Single 3.3V power supply, low power consumption, <1.5W</li>

- All-metal housing for superior EMI performance, low Near-End Crosstalk(NEXT)

- Precision process control for minimization of pair-to-pair skew

- Pull-to-release latch for easy installation

- RoHS compliant

# **Applications**

- InfiniBand-SDR, DDR, QDR

- Computer cluster cross-connect

- Switches, Routers, and HBA's

- Enterprise Data Center

- High Performance Computing(HPC) & Storage

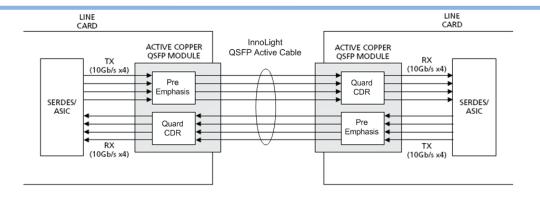

Figure1: Application in System

### 1. GENERAL DESCRIPTION

The InnoLight TC-QQCOx-V00 is specifically designed to allow the end-user an active cable connection solution between ports based on QSFP connectivity, respectively. The cable is plugand-play into these powered ports and provides the customer with all the advantages of a cost effective & easy to handle high speed connection. The transmitter side accepts electrical input signals which are voltage compatible with both Low Voltage Positive Emitter Coupled Logic (LVPECL) and Current Mode Logic (CML) levels. All input data signals are differential and are internally terminated. The receiver side recovers the parallel electrical input signals via a quad CDR into clear-edge parallel electrical output signals. The outputs electrical signals of receive side are voltage compatible with Current Mode Logic (CML) levels. All data signals are differential and support a data rate up to 10Gbps per channel. All transmitter signals and receiver signals are AC coupled internally on both modules ends.

The figure on the next page, presents a detailed functional block diagram of the QSFP module with corresponding external connection pins.

A single +3.3V power supply is required to power up the module. Both power supply pins VccTx and VccRx are internally connected and should be applied concurrently. As per MSA specifications the module offers 7 low speed hardware control pins (including the 2-wire serial interface): ModSelL, SCL, SDA, ResetL, LPMode, ModPrsL and IntL.

Module Select (ModSelL) is an input pin. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP modules on a single 2-wire interface bus – individual ModSelL lines for each QSFP module must be used.

Serial Clock (SCL) and Serial Data (SDA) are required for the 2-wire serial bus communication

interface and enable the host to access the QSFP memory map.

The ResetL pin enables a complete module reset, returning module settings to their default state, when a low level on the ResetL pin is held for longer than the minimum pulse length. During the execution of a reset the host shall disregard all status bits until the module indicates a completion of the reset interrupt. The module indicates this by posting an IntL (Interrupt) signal with the Data\_Not\_Ready bit negated in the memory map. Note that on power up (including hot insertion) the module should post this completion of reset interrupt without requiring a reset.

Low Power Mode (LPMode) pin is used to set the maximum power consumption for the module in order to protect hosts that are not capable of cooling higher power modules, should such modules be accidentally inserted.

Module Present (ModPrsL) is a signal local to the host board which, in the absence of a module, is normally pulled up to the host Vcc. When a module is inserted into the connector, it completes the path to ground though a resistor on the host board and asserts the signal. ModPrsL then indicates a module is present by setting ModPrsL to a "Low" state.

Interrupt (IntL) is an output pin. When "Low", it indicates a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL pin is an open collector output and must be pulled to the Host Vcc voltage on the Host board.

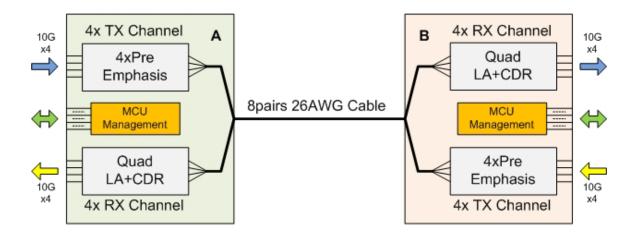

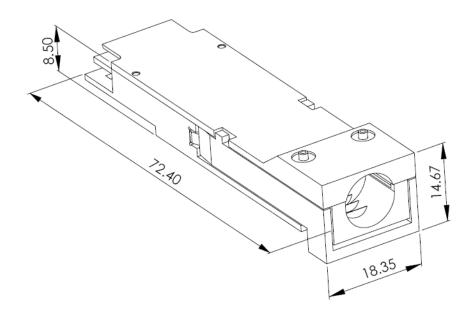

## 2. QSFP Copper Design Structure

InnoLight TR-QQCOZ-N00 active copper cable includes one pair (A-B) QSFP modules connected by 26AWG cable which have 8 pair differential cables inside, the cable lengths are 10M, 13M to 15M, three different types.

| Part Number  | Diameter<br>(mm) | Max Length (m) |

|--------------|------------------|----------------|

| TC-QQCOS-V00 | 7.11             | 10             |

| TC-QQCOM-V00 | 7.11             | 13             |

| TC-QQCOL-V00 | 7.11             | 15             |

## 3. Absolute Maximum Ratings

| Parameter                            | Symbol  | Min  | Max        | Unit | Note |

|--------------------------------------|---------|------|------------|------|------|

| Storage Temperature                  | Tst     | -40  | 125        | degC |      |

| Relative Humidity (non-condensation) | RH      | 1    | 85         | %    |      |

| Operating Case Temperature           | Торс    | -40  | 85         | degC | 1    |

| Supply Voltage                       | VCC3    | -0.3 | 3.6        | V    |      |

| Voltage on LVTTL Input               | Vilvttl | -0.3 | VCC3 + 0.2 | V    |      |

**NOTE**: Stress above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not applied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **4. Recommended Operating Conditions and Supply Requirements**

| Parameter                          | Symbol | Min   | Max   | Unit |

|------------------------------------|--------|-------|-------|------|

| Operating Case Temperature         | Торс   | -40   | 85    | degC |

| Relative Humidity (non-condensing) | Rhop   | -     | 85    | %    |

| Power Supply Voltage               | VCC3   | 3.135 | 3.465 | V    |

| Power Supply Current               | ICC3   | -     | 750   | mA   |

| Total Power Consumption            | Pd     | -     | 2.0   | W    |

# 5. DC Low Speed Control and Alarm Signals Electrical Interface

| Parameter         | Conditions     | Symbol | Min               | Тур. | Max               | Units |

|-------------------|----------------|--------|-------------------|------|-------------------|-------|

| Supply Current    | @ VCCT         | IVCC   |                   | 450  | 570               | mA    |

| Power Consumption |                |        |                   | 1.48 | 1.88              | W     |

|                   | Host Vcc Range |        | 0                 |      | 0.4               |       |

| ModPrsl and IntL  | 2V – 3.47V     | VOH    | Host_Vcc<br>- 0.5 |      | Host_Vcc +<br>0.3 |       |

| LPMode, Reset,    | Low Voltage    | VIL    | 0.3               |      | 0.8               |       |

| ModeSelL          | ModeSelL TTL   |        | 2                 |      | VccT + 0.3        | V     |

|                   |                | VIL    | 0.3               |      | VccT*0.3          | V     |

| SCL, SDA          | Host Vcc Range | VIH    | VccT*0.7          |      | VccT + 0.5        |       |

|                   | 3.14V – 3.47V  | VOL    | 0                 |      | 0.4               |       |

|                   |                | VOH    | Host_Vcc<br>- 0.5 |      | Host_Vcc +<br>0.3 |       |

# **6. Module Transmitter Single Channel Input Characteristics**

| Parameter                                 | Conditions | Symbol | Min  | Тур. | Max  | Units       |

|-------------------------------------------|------------|--------|------|------|------|-------------|

| Nominal Data Rate                         |            | DR     | 2.49 | 10   | 11.3 | Gbps        |

| Reference Differential Input<br>Impedance |            | Zd     | 80   | 100  | 120  | Ω           |

| Input AC Common Mode Input<br>Voltage     |            |        | 0    |      | 20   | mV<br>(RMS) |

| Differential Input Voltage Swing          |            | VID    | 100  |      | 1200 | mV          |

# 7. Module Receiver Single Channel Output Characteristics

| Parameter                                  | Conditions                          | Symbol   | Min  | Тур. | Max  | Units |

|--------------------------------------------|-------------------------------------|----------|------|------|------|-------|

| Nominal Data Rate                          |                                     | DR       | 2.49 | 10   | 11.3 | Gbps  |

| Reference Differential Output<br>Impedance |                                     | Zd       | 80   | 100  | 120  | Ω     |

| Differential Output Amplitude              | RLoad = 1000hm,<br>Differential     | VOSPP    | 370  |      | 800  | mV    |

| Output Rise and Fall time                  | 20% to 80%                          | tRH, tFH | 30   |      |      | ps    |

| Receiver Output Deterministic Jitter       |                                     | DJ       |      |      | 10   | ps    |

| Receiver Output Total Jitter               | @10Gbps<br>(BER 10 <sup>-12</sup> ) | TJ       |      |      | 25   | ps    |

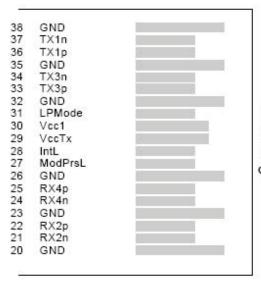

## 8. Pin Assignments and Descriptions

2 TX2n TX2p GND 4 5 6 7 8 TX4n TX4p GND Card ModSelL ResetL 9 Edge 10 VccRx SCL 11 SDA 12 13 GND RX3p 14 RX3n 15 GND 16 RX1p 17 RX1n GND 18 19

GND

Top Side Viewed from Top

Bottom Side Viewed from Bottom

| PIN | Logic      | Symbol  | Name/Description                     | Note |

|-----|------------|---------|--------------------------------------|------|

| 1   |            | GND     | Ground                               | 1    |

| 2   | CML-I      | Tx2n    | Transmitter Inverted Data Input      |      |

| 3   | CML-I      | Tx2p    | Transmitter Non-Inverted Data        |      |

| 3   | CIVIL-I    | ΙλΖμ    | output                               |      |

| 4   |            | GND     | Ground                               | 1    |

| 5   | CML-I      | Tx4n    | Transmitter Inverted Data Input      |      |

| 6   | CML-I      | Tx4p    | Transmitter Non-Inverted Data output |      |

| 7   |            | GND     | Ground                               | 1    |

| 8   | LVTLL-I    | ModSelL | Module Select                        |      |

| 9   | LVTLL-I    | ResetL  | Module Reset                         |      |

| 10  |            | Vcc Rx  | + 3.3V Power Supply Receiver         | 2    |

| 11  | LVCMOS-I/O | SCL     | 2-Wire Serial Interface Clock        |      |

| 12  | LVCMOS-I/O | SDA     | 2-Wire Serial Interface Data         |      |

| 13  |            | GND     | Ground                               |      |

| 14  | CML-O      | Rx3p    | Receiver Non-Inverted Data Output    |      |

| 15  | CMLO       | Rx3n    | Receiver Inverted Data Output        |      |

| 16  |            | GND     | Ground                               | 1    |

| 17  | CMLO       | Rx1p    | Receiver Non-Inverted Data Output    |      |

| 18  | CMLO       | Rx1n    | Receiver Inverted Data Output        |      |

| 19  |            | GND     | Ground                               | 1    |

| 20  |            | GND     | Ground                               | 1    |

| 21  | CMLO       | Rx2n    | Receiver Inverted Data Output        |      |

| 22  | CMLO       | Rx2p    | Receiver Non-Inverted Data Output    |      |

| 23  |            | GND     | Ground                               | 1    |

| 24  | CMLO       | Rx4n    | Receiver Inverted Data Output        | 1    |

| 25  | CMLO       | Rx4p    | Receiver Non-Inverted Data Output    |      |

| 26  |            | GND     | Ground                               | 1    |

| 27  | LVTTLO     | ModPrsL | Module Present                       |      |

| 28  | LVTTLO     | IntL    | Interrupt                            |      |

| 29  |            | Vcc Tx  | +3.3 V Power Supply transmitter      | 2    |

| 30  |            | Vcc1    | +3.3 V Power Supply                  | 2    |

| 31  | LVTTLI     | LPMode  | Low Power Mode                       |      |

| 32  |            | GND     | Ground                               | 1    |

| 33  | CMLI       | Тх3р    | Transmitter Non-Inverted Data Input  |      |

| 34  | CMLI       | Tx3n    | Transmitter Inverted Data Output     |      |

| 35  |            | GND     | Ground                               | 1    |

| 36  | CMLI       | Tx1p    | Transmitter Non-Inverted Data Input  |      |

| 37  | CMLI       | Tx1n    | Transmitter Inverted Data Output     |      |

| 38  |            | GND     | Ground                               | 1    |

- GND is the symbol for signal and supply (power) common for QSFP modules. All are common within the QSFP module and all module voltages are referenced to this potential otherwise noted. Connect these directly to the host board signal common ground plane.

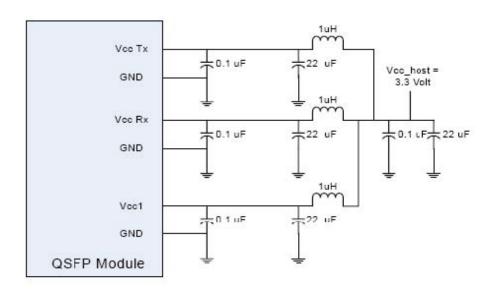

- 2. Vcc Rx, Vcc1 and Vcc Tx are the receiver and transmitter power suppliers and shall be applied concurrently. Recommended host board power supply filtering is shown below. Vcc Rx, Vcc1 and Vcc Tx may be internally connected within the QSFP transceiver module in any combination. The connector pins are each rated for a maximum current of 500mA.

### 9. Recommended power supply filtering Example of QSFP Host board schematics.

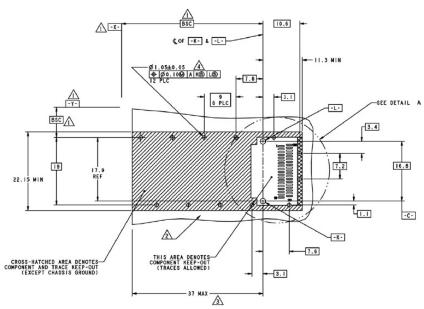

## 10. Recommended PCB layout

A typical host board mechanical layout for attaching the QSFP transceiver is presented below. The recommended host electrical connector should be a 38-pin IPASS right angle connector assembly (example: Tyco PN: 1761987-9) and the cage assembly should be QSFP single cage (example: Tyco PN: 1888617-1).

↑ DATUM -X- AND -Y- ESTABLISHED BY CUSTOMER'S FIDUCIAL

↑ DATUM -A- IS TOP SURFACE OF HOST BOARD.

↑ LOCATION OF EDGE OF PCB IS APPLICATION SPECIFIC.

↑ FINISHED HOLE SIZE.

CENTERLINE OF PAD.

SURFACE TRACES PERMITTED

WITHIN THIS LENGTH.

INDICATED HOLES ARE OPTIONAL.

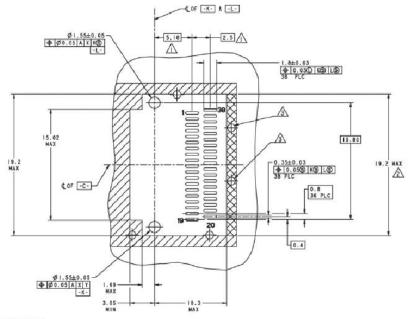

# **QSFP Copper Module Outline for System Design**

| USA                        | China                                  |

|----------------------------|----------------------------------------|

| InnoLight Technology Corp. | InnoLight Technology (Suzhou) Ltd.     |

| Tel: (408) 838-8769        | Tel: (0512) 6299-4707                  |

| Fax: (408) 777-8091        | Fax: (0512) 6299-4515                  |

| Email: omok@innolight.com  | Email: jyang@innolight.com             |

| Add:                       | Add:                                   |

| 3 Results Way, Cupertino   | A311 Section2 International Science    |

| CA 95014                   | Park 1355 Jinji Lake Ave., Suzhou SIP, |

| United States              | Jiangsu 215021 China                   |

# **Contact Information**